VIAVI - Xgig 4K4 Analyzer Platform for PCI Express 4.0

-

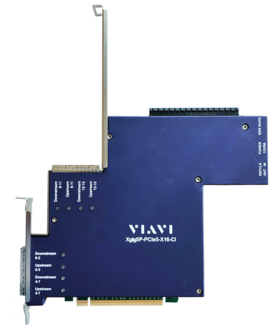

16GTps, PCIe 4.0 data rate operation. Fully compatible with lower PCIe data rates of 2.5, 5.0 and 8.0GTps

-

Link widths up to 4-lanes

-

32GB memory (16GB Up Stream and 16GB Down Stream)

-

Memory segmentation for capture of multiple traces

-

Host-Client connection for remote debugging using Ethernet or local debugging using USB

-

SMB capture and trigger for NVMe Management Interface (NVMe-MI) observability

-

Decodes all PCIe and NVMe traffic at all layers of the stack including the TLP, DLLP, and PHY layer blocks

-

Trigger and Search events include training sequences, ordered sets, queue pairs, PRPs, Scatter/Gather Lists (SGL), SMB, etc.

-

Full support of LTSSM for PCI Express

-

Multicolored LEDs on the front panel specify link speed, lane width and performance

-

Field replaceable modular fan and power supply assemblies

-

Works with Interposers for CEM slots, Flying-Lead probes, U.2 (SFF-8639), M.2, SFF-8674, OCulink, EDSFF and others

-

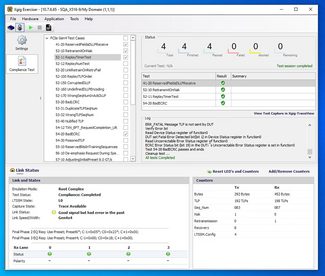

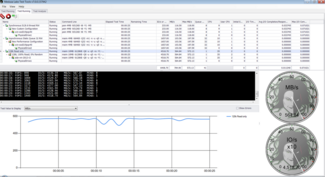

Supported by Xgig tool suite including Trace Control, Expert and Serialytics

The Xgig 4K4 platform provides protocol analysis for PCIe and NVMe traffic at all layers of the stack.

The Xgig® 4K4 Protocol Analyzer expands the family of VIAVI protocol analysis products targeting storage and other applications. It provides advanced PCIe and NVMe level trigger and search capabilities designed to reduce debug and problem resolution down time. Interposer autotuning automatically restores signal integrity by reducing insertion loss in both directions, greatly reducing set-up time. Analysis will alert the user to all protocol errors at every layer of the PCIe stack, including state and substate level errors within the LTSSM viewer.

Application

- Full-speed data capture and error injection, enabling detailed functional and performance analysis of PCIe protocol

- Used for IC development, debug and validation, subsystem and system-level testing, firmware and driver development and validation, and performance analysis

- Full-speed data capture and error injection, enabling detailed functional and performance analysis of PCIe protocol

- Used for IC development, debug and validation, subsystem and system-level testing, firmware and driver development and validation, and performance analysis

Benefits

- The Tap ports enable enable multi-analyzer configurations using a single Interposer in the channel

- Cascade up to four Xgig time-correlated trace captures

More Product Information

Test & Measurement

Download Line Card

Document

Embedded

Download Line Card

Document