Webinar

Optimizing Transmitter Test and Margin Analysis of 16+ Gb/s Signals

Join Teledyne LeCroy for our new three-part webinar series to learn more about how to accelerate and improve testing of PCIe® v. 4.0 and 5.0, USB4™, Thunderbolt™ 4, and DisplayPort™ 2.0 serial data links.

Nov. 19 - Part One: Identifying and Debugging PCIe Link Equalization Problems

Dec. 3 - Part Two: Simplifying Receiver Calibration and Test of 16+ Gb/s Serial Data Links

Dec. 16 - Part Three: Optimizing Transmitter Test and Margin Analysis of 16+ Gb/s Signals

Join us for Part Three: Optimizing Transmitter Test and Margin Analysis of 16+ Gb/s Signals

High-speed serial link transmitter testing can be optimized with the right tools, and valuable circuit design operating margin information can be extracted.

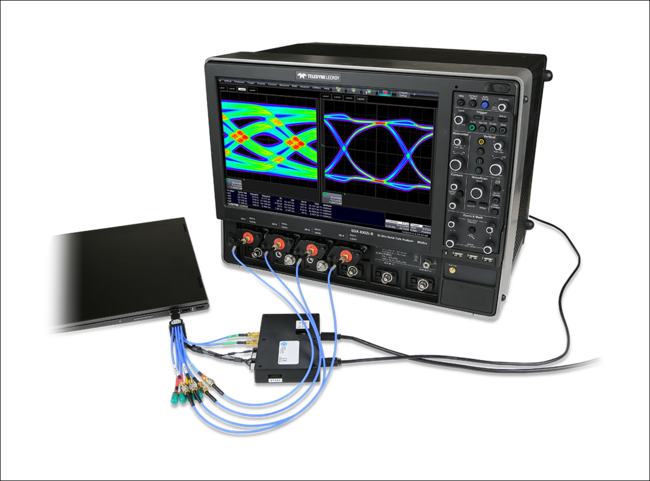

This webinar will provide an overview of a typical high-speed serial data transmitter test using USB4 as an example. We will synthesize a high-speed serial data signal, use a real-time oscilloscope to analyze the signal at a virtual receiver, and compare the virtually-received signal to a live signal. We will review signal integrity margin analysis and jitter, eye diagram, IsoBER contour and crosstalk eye measurements.

Who should attend?

- Signal Integrity Engineers

- Design and Validation Test Engineers

Presenters:

Mike Engbretson, Product Marketing Manager and John Smith, HSS Business Development Manager

Click here for details on Part One

Click here for details on Part Two

Can't attend live? Register anyway, and we will send you the recording and slides afterward.